# AUSLEGESCHRIFT 1099767

V 15806 IX/42m

ANMELDETAG: 21. JANUAR 1959

BEKANNTMACHUNG DER ANMELDUNG UND AUSGABE DER

AUSLEGESCHRIFT: 16. FEBRUAR 1961

1

Die Erfindung betrifft ein Rechenwerk mit zwei hintereinandergeschalteten Binär-Addiatoren-Subtraktoren mit nachgeschalteten Schiebelinien für die Addition bzw. Subtraktion zweier Dezimalzahlen mit Korrektur der in einem Binär-Addiator-Subtraktor gebil- 5 deten Summe oder Differenz zweier als Tetraden verschlüsselter Dezimalzahlen, wobei sowohl die Dezimalzahlen als auch die Dualziffern der Tetraden nacheinander in das Rechenwerk einlaufen.

Die Schwierigkeiten für die Ausführung der Rechen- 10 operationen bei einer reinen dezimalen Serienrechenmaschine liegen in der Korrektur der addierten Tetraden. Wird nämlich eine Summe zweier nach der direkten Verschlüsselung verschlüsselter Tetraden gebildet, die größer als Neun ist, so werden im Binäraddiator 15. erst die bis zur Fünfzehn reichenden Tetradenkombinationen gebildet, die als Pseudodezimalen bezeichnet werden. Es kann erst dann der letzte Entscheid darüber, wie zu korrigieren ist, getroffen werden, wenn die Dualstellen der Summentetrade aus dem Addiator 20 ausgelaufen sind. Der normale Rechenvorgang einer Serienrechenmaschine vollzieht sich so, daß die Dualstellen der Operanden (Augend, Addend, Multiplikand usw.) aus den Registern, z.B. Umlaufden und die Dualstelle des Ergebnisses wieder in das Speicherwerk einläuft. Demselben Vorgang sind deshalb die nächsten Dualziffern unterworfen. Die vorige Dualstelle ist dann wieder im Speicher eingetragen, benutzt werden können, und somit dem Rechenwerk verlorengegangen. Soll sie auch weiterhin für die Rechnung erhalten bleiben, so ist sie in einem dauernd zugänglichen besonderen Speicher zwischenzuspei-Kippschaltungen, die zu einer Kette zusammengeschaltet sind. Es ist bereits eine Korrekturmöglichkeit bekanntgeworden, die so arbeitet, daß in einem Binäraddiator die noch zu korrigierende Summentetrade gebildet wird, diese in eine Verzögerungs- 40 leitung läuft, von der am Ende des Tetradenauslaufes die Dualstellen in paralleler Form einem Hilfszählwerk zugeführt werden, das einen weiteren Addiator beeinflußt, durch den die Tetrade zur Korrektur beim dieser Schaltung ist, daß ein entsprechend der Korrekturerfordernis steuerbares Hilfszählwerk vorhanden ist, das durch logische Verknüpfungskreise gesteuert werden muß. Dieses gesteuerte Hilfszählwerk ist sehr aufwendig. Ein weit wesentlicherer Nachteil 50 der bekannten Korrekturschaltung ist außerdem, daß mit ihr nur eine Korrektur bei Addition ausgeführt wird. Es ist weiterhin eine Rechenvorrichtung bekanntgeworden, welche zwei hintereinandergeschaltete

## Rechenwerk

### Anmelder:

VEB Elektronische Rechenmaschinen Wissenschaftlicher Industriebetrieb Karl-Marx-Stadt, Karl-Marx-Stadt W 30, Zwickauer Str. 219

> Dipl.-Ing. Walter Kasper, Karl-Marx-Stadt, ist als Erfinder genannt worden

Addiatoren mit nachgeschalteten Schieberegistern beinhaltet, bei der die Korrektur so erfolgt, daß immer die unkorrigierte Summe gebildet wird. Ob es sich speichern, auslaufen, im Rechenwerk verarbeitet wer- 25 bei der gebildeten Summe um eine Pseudodezimale handelt, wird in Koinzidenzkreisen festgestellt. Bei Vorhandensein einer Pseudodezimale wird der zweite Addiator eingeschaltet und der entsprechende Korrekturwert hinzugefügt. Diese Einrichtung hat den Nachfür die z.B. Bahnen einer bekannten Magnettrommel 30 teil, daß zur Korrektur zwei Tetradenzeiten bei tetradischer Verschlüsselung der Dezimalzahlen erforderlich sind und daß die Schaltungsanordnung zur Bildung des Korrekturentscheids sehr aufwendig ist.

Aufgabe der Erfindung ist es, eine Korrekturschalchern. Solche Speicher sind unter anderem bistabile 35 tung für Serienrechenwerke, welche sowohl Addition als auch Subtraktionen ausführen, unter Vermeidung der aufgezeigten Nachteile zu schaffen.

Die erfindungsgemäße Lösung besteht darin, daß die unkorrigierte und die korrigierte Summe gleichzeitig gebildet werden, indem einem Eingang des Korrektur-Addiator-Subtraktors ungesteuert ein Korrekturwert zugeleitet wird und ein im Korrektur-Addiator-Subtraktor erzeugter und gespeicherter Übertrag durch Umschalten des Übertrag-Flip-Flops Auslauf aus der Verzögerungslinie läuft. Ein Nachteil 45 mit einer Impulsfolge den Übertrags-Flip-Flop vom Haupt-Addiator-Subtraktor einschaltet, wodurch der Übertrag in die nächste Tetrade eingetragen wird und über logische Schaltkreise, die den logischen Ausdruck

$$k_e = S_1 (S_2 + S_3) \ddot{u}_{n-1}$$

und dessen Negation realisieren, den Auslauf der korrigierten oder unkorrigierten Summe bzw. Differenz aus den Schieberegistern steuert.

Die Erfindung wird an Hand eines Ausführungsbeispiels näher erklärt. In der Zeichnung bedeutet

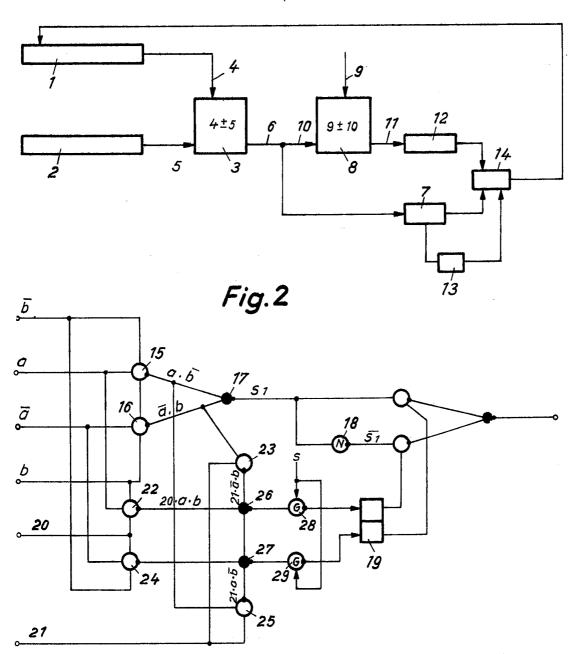

Fig. 1 ein Blockschaltbild des Ziffernweges mit der Korrektureinrichtung,

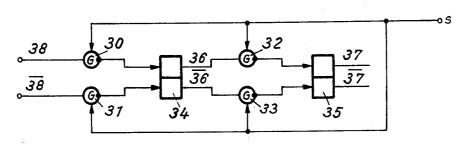

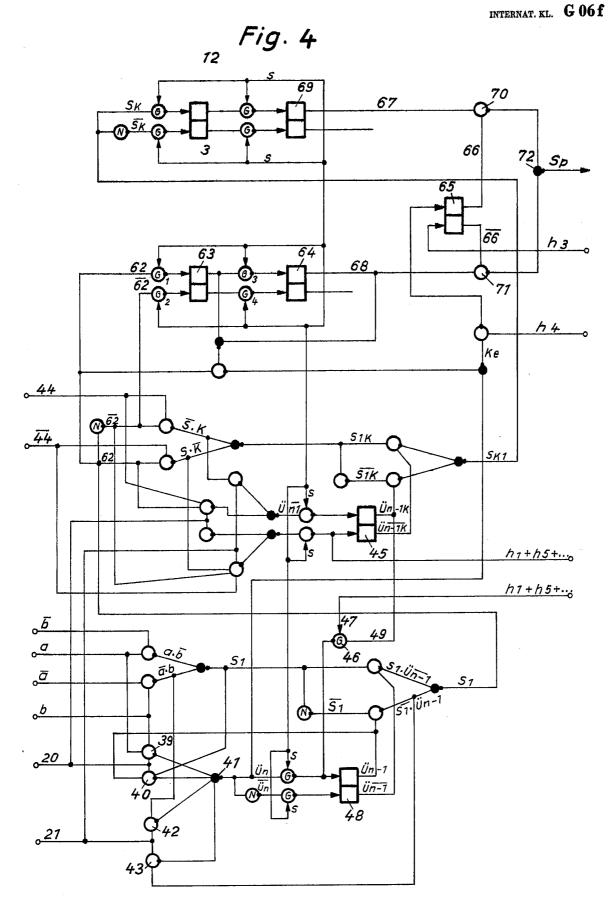

Fig. 2 einen an sich bekannten Addiator-Subtraktor, 5 Fig. 3 ein Schieberegister,

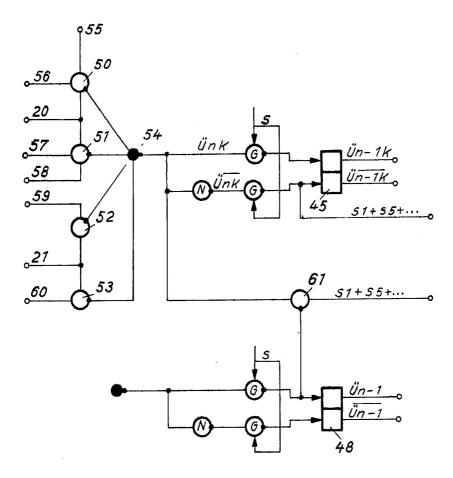

Fig. 4 eine Ausführungsform der gesamten logischen Schaltung,

Fig. 4,1 und 4,2 geänderte Ausführungsformen der Schaltung nach Fig. 4,

Fig. 5 einen Konjunktionsknoten, Fig. 6 einen Disjunktionsknoten.

Es sind zwei Tetraden  $x_1$  und  $x_2$  zu addieren oder zu subtrahieren. Die Dezimalziffern sind beispielsweise direkt dual verschlüsselt, d. h. in der Form 15  $z_i = x_i$  ( $z_i$  ist die Dezimalziffer,  $x_i$  dieselbe Ziffer dual dargestellt). In Fig. 1 ist dargestellt, wie von zwei Umlaufspeicherbahnen 1 und 2 die beiden Summanden in den Addiator-Subtraktor 3 laufen, nach Addiatoreingang 4 der Augend und nach Addiatoreingang 5 20 der Addend. Bei Subtraktion läuft nach Eingang 4 der Minuend und nach Eingang 5 der Subtrahend. Der Addiatorauslauf bei Ausgang 6 ist in das Verschieberegister 7 und in den Korrektur-Addiator-Subtraktor 8 mit den Eingängen 9 und 10 geführt. 25 Die aus dem Korrekturaddiator, Ausgang 11, auslaufende Summe gelangt in das Verschieberegister 12. Ein Korrekturentscheid 13 überprüft die Summentetrade, ob zu korrigieren ist oder nicht, und beeinflußt eine Auswahl 14, die entweder die korrigierte 30 oder unkorrigierte Summentetrade auswählt. Der Addiator 3 und der Korrekturaddiator 8 sind z. B. reine Dualaddiatoren nach Fig. 2. Die Summe zweier Dualzahlen ergibt sich durch den logischen Ausdruck  $a \cdot \overline{b} + \overline{a} \cdot b$  mit

·-Zeichen für die Konjunktion (Und-Schaltung), +-Zeichen für die Disjunktion (Oder-Schaltung),  $\bar{b}$ -Zeichen für die Negation von b (Negator).

Zwei Und-Schaltungen 15 und 16 in Fig. 2, die durch innen weiß gelassene Kreise dargestellt sind, und eine Oder-Schaltung 17, die durch den innen schwarz ausgezogenen Kreis dargestellt ist, liefern die Teilsumme  $S_1$  der dualen Summanden a und b. 45 Die Konjunktionen  $\bar{a} \cdot b$  und  $a \cdot \bar{b}$  können auch zur Übertragsbildung bei der Subtraktion ausgenutzt werden. Es werden sowohl die Teilsumme  $S_1$  als auch deren Negation  $\overline{S}_1$  benötigt. Die negierte Teilsumme  $\overline{S}_1$  erhält man aus der Teilsumme S<sub>1</sub> durch Zwischenschal- 50 ten des Negators 18 in Fig. 2. Bezüglich der gezeichneten Schaltungssymbole ist noch zu sagen, daß der Ausgang der Verknüpfungskreise stets durch einen Punkt gekennzeichnet ist. Zur Teilsumme  $S_1$  der beiden Dualzahlen ist außerdem der Übertrag  $\ddot{u}_{n-1}$  aus 55 der vorigen Stelle zu addieren. Die endgültige Dualstelle der Summe liefert also erst der logische Ausdruck

$$S = S_1 \cdot \overline{\ddot{u}_{n-1}} + \overline{S}_1 \cdot \ddot{u}_{n-1}.$$

$\ddot{u}_{n-1}$  ist der Übertrag aus der vorigen Stelle. Der Übertrag wird z. B. vom Übertrags-Flip-Flop 19 geliefert, der den Übertrag um eine Dualstelle verzögert. Bei der Subtraktion ist die Summe S genauso gebildet, nur der Übertrag wird anders erzeugt. Zwei 65 Steuerleitungen 20 und 21 befehlen, ob zu addieren oder zu subtrahieren ist. Bei Addition führt die Steuerleitung 20 eine der dualen Eins entsprechende Schaltgröße L und die Steuerleitung 21 eine der

Subtraktion ist es umgekehrt. Wenn die Steuerleitung 20 die Schaltgröße L führt, schaltet die Konjunktion  $a \cdot b$  den Übertrags-Flip-Flop ein und erst bei  $\bar{a} \cdot \bar{b}$ wieder aus. Zu diesem Zweck sind die Und-Schaltungen  ${f 20} \cdot a \cdot b$  und  ${f 20} \cdot \overline{a} \cdot \overline{b}$  vorhanden. Wenn die Steuerleitung 21 die Schaltgröße L führt, schaltet  $21 \cdot \bar{a} \cdot b$ den Übertrags Flip-Flop ein und  $21 \cdot a \cdot \overline{b}$  wieder aus. Die beiden Und-Schaltungen für jede Flip-Flop-Stellung 22 und 23 sowie 24 und 25 sind über eine Oder-Schaltung 26 bzw. 27 zusammengeführt und mit dem Schalteingang eines Impulsgatters 28 bzw. 29 verbunden. Zeigt am Schalteingang das Gatter die Schaltgröße L und gelangt als zusätzliche Bedienung über den mit dem Pfeil gekennzeichneten Impulseingang der Synchronisierimpuls s an das Gatter, dann wird die zugehörige Flip-Flop-Seite, die mit dem durch den Punkt gekennzeichneten Ausgang des Gatters verbunden ist, auf L gestellt. Der Synchronisierimpuls s erscheint zu Anfang jeder Dualziffernzeit und leitet somit die Ziffernschaltgrößen L oder 0 ein. Als Ausführungsbeispiel für die Verzögerungsleitung ist in Fig. 3 die bekannte, über Impulsgatter 30, 31, 32 oder 33 mit Synchronisierimpulsen s weiterzuschaltende Flip-Flop-Kette 34 und 35 gezeigt. Diese Impulse sind sehr kurzzeitig und dauern nur über einen Bruchteil der Ziffernzeit an. Jeder Synchronisierimpuls s führt den Inhalt des vorhergehenden Flip-Flops in den nächsten über. Wenn der Flip-Flop 34 an seinem Ausgang 36 eine Schaltgröße des Wertes L liefert und der Flip-Flop 35 an seinem Ausgang 37 eine Schaltgröße des Wertes 0 hat, liefern demnach die negierten Ausgänge 36 und 37 die Schaltgrößen 0 und L. Dem Eingang wird mit 38=0 bzw. 38=L zur erforderlichen Dualstellenzeit eine Null mitgeteilt. Für den Synchronisierimpuls s am Ende dieser Dualstellenzeit sind somit die Gatter 31 und 32 geöffnet, da nur an ihren Schalteingängen eine Schaltgröße des Wertes L anliegt. Der Synchronisierimpuls s schaltet den Flip-Flop 34 aus und den Flip-Flop 35 ein, wodurch die L um ein Glied weiterrückt. Zur näheren Erläuterung der in Fig. 4 gezeigten Gesamtschaltung muß erst angegeben werden, wann zu korrigieren ist und welcher Wert additiv oder subtraktiv hinzuzufügen ist. Bei der direkten Verschlüsselung ist eine Korrektur immer dann notwendig, wenn eine der

> L 0 L L L L L 0 L L 0 L

sechs Pseudodezimalen

oder ein Übertrag in die nachfolgende Tetrade erscheint. Bei Addition wird beispielsweise 5+5 nicht eine Null als Summe und eine Eins als Übertrag in 60 die nächsthöhere Stelle ergeben, sondern Pseudodezimale 10=L0L0. Zur Erreichung des wirklichen Wertes 1 und 0 ist +6 dual zu addieren. Zum Beispiel liefert 8+9 dual tetradisch addiert eine L als Summentetrade und eine L als Übertrag in die nächste Tetrade. Es ist ebenfalls +6 zu addieren. Bei Subtraktion liefert z. B. 7-9 eine Pseudodezimale, nämlich 14=LLL0, und einen Übertrag in die nächste Stelle. Es ist hier mit −6 zu korrigieren, um den richtigen Wert 8 und einen Übertrag zu erhalten. dualen Null entsprechende Schaltgröße 0. Bei der 70 Der Fall, daß der Subtrahend größer als der um »6«

vermehrte Minuend ist. liefert nur einen Übertrag, aber keine Pseudodezimale. Auch hier ist mit -6 zu korrigieren. Man kann somit für die Subtraktion sogar nur eine einzige Korrekturbedingung ableiten, indem immer dann mit -6 zu korrigieren ist, wenn ein Übertrag in der nächsten Tetrade erscheint. In Fig. 4 sind zunächst die beiden binären Addiator-Subtraktoren gezeichnet, wobei allerdings im Ausführungsbeispiel für den Summenaddiator der Übertrag etwas anders erzeugt wird Der gesteuerte Über- 10 trag für die Addition ist nach dem dafür geltenden logischen Ausdruck

$$\ddot{u}_{n+} = a \cdot b \cdot 20 + S_1 \cdot \ddot{u}_{n-1} \cdot 20$$

durch zwei dreifache Und-Schaltungen 39 und 40, die 15 in einer Oder-Schaltung 41 zusammengeführt sind, gebildet. Für den gesteuerten Übertrag bei der Subtraktion gilt der logische Ausdruck

$$\ddot{u}_{n-} = \bar{a} \cdot b \cdot 21 + \bar{S}_1 \cdot \ddot{u}_{n-1} \cdot 21$$

Damit ergibt sich der Gesamtübertrag für Summe und Differenz zu

$$\ddot{u}_{nges} = a \cdot b \cdot 20 + \bar{a} \cdot b \cdot 21 + S_1 \cdot \ddot{u}_{n-1} \cdot 20 + \bar{S}_1 \cdot \ddot{u}_{n-1} \cdot 21$$

und wird durch vier Und-Schaltungen 39, 40, 42 und 25 43, die in einer vierfachen Oder-Schaltung 41 zusammengeführt sind, realisiert. Die Schaltungen können z. B. die bekannten Diodenknoten nach Fig. 5 und 6 sein. Zwei Und-Schaltungen 42 und 43 für den Ubertrag sind nur zweifach, da  $\overline{a} \cdot b$  und  $\overline{S}_1 \cdot \ddot{u}_{n-1}$  bereits für die Bildung der Summe benötigt werden. Der Korrektur-Addiator-Subtraktor gleicht dem bereits vorher beschriebenen. Dem Eingang 44 des Korrekturaddiators wird von der Impulszentrale ein Schaltmäander der Form zugeführt, daß er während 35 zweier Dualstellenzeiten die Schaltgröße 0 annimmt. Diese Folge wiederholt sich ständig. Sie wird im nicht dargestellten Steuerteil erzeugt, da sie auch an anderen Maschinenstellen benötigt wird und somit keinen zusätzlichen Aufwand bringt. Ferner haben 40 die beiden Schaltgrößen des Wertes L die beiden mittleren Ziffernplätze jeder Tetrade einzunehmen, wodurch man erkennt, daß damit laufend der Korrekturwert 6 in den Addiator-Subtraktor eingegeben wird, der bei Addition addiert, bei Subtraktion aber, 45 wie die Steuerung über die Engänge 20 und 21 es bewirkt, subtrahiert wird. Der Korrekturaddiator wird also genauso entsprechend der Operation gesteuert wie der Hauptaddiator. Die Summentetrade läuft außer durch den Korrekturaddiator auch in das 50 Schieberegister 7. Die korrigierte Summentetrade läuft in das Schieberegister 12.  $S_1$ ,  $S_2$ ,  $S_3$  und  $S_4$  sind die vier Stellen der Summentetrade ( $S_4$  hat in diesem Beispiel die niedrigste Stellenwertigkeit),  $\ddot{u}_n$  ist der Theorem in die neuhfolgende Totrade im Summen. Übertrag in die nachfolgende Tetrade im Summen- 55 addiator. Daraus ergibt sich der Korrekturentscheid durch schaltungsmäßige Realisierung des logischen Ausdrucks

$$\begin{split} K_e &= S_1 \cdot S_2 + S_1 \cdot S_3 + \ddot{u}_n \text{ (Korrekturentscheid)} \\ &= S_1 \cdot (S_2 + S_3) + \ddot{u}_n. \end{split}$$

Die Bedingung  $S_1 \cdot S_2 + S_1 \cdot S_3$  ergibt sich aus den Pseudodezimalen, die Bedingung  $\ddot{u}_{n-1}$  aus dem Übertrag in die nächste Stelle des Summenaddiators. Bei 65 Addition kann durch additives Hinzufügen einer Sechs zur Pseudodezimale ein gültiger Übertrag in die nächste Tetrade entstehen. Dieser Übertrag kann, wenn die nächste Summentetrade eine Neun ist, die

addition sein, indem die Pseudodezimale 10=L0L0 entsteht. Um zu vermeiden, daß dieser im Korrekturaddiator erzeugte Übertrag in der nächsten Tetrade gesondert verarbeitet werden muß, was auch für Werte ungleich Neun der Summentetrade erforderlich ist, wird am Korrekturaddiator grundsätzlich kein Übertrag in die nächste Tetrade geschickt. Die aus der Impulszentrale kommende Impulsfolge  $h_1 + h_5 + \cdots$  die zu Beginn jeder Tetradenzeit einen Impuls liefert, löscht dann am Korrekturaddiator den Übertrags-Flip-Flop 45. Gleichzeitig wird, wenn ein Übertrag vorhanden war, über ein Gatter 46, an dessen Impulseingang 47 diese Impulsfolge liegt, der Übertrags-Flip-Flop 48 des Hauptaddiators eingeschaltet. Am Schalteingang 49 des Gatters 46 liegt die Schaltgröße  $\ddot{u}_{n-1\,k}$ , nämlich der seit Beginn der neuen Tetradenzeit festliegende Übertrag in diese Tetrade. Daraus erkennt man, daß die Impulsfolge  $h_1 + h_5 + \cdots$ sich nicht mit dem ersten Synchronisierimpuls s jeder Tetrade deckt, sondern etwas später erscheint, nachdem die von s geschalteten Zustände bereits völlig eingeschwungen sind. Zweckmäßig liegen die  $h_1$ -Impulse in der Mitte zwischen zwei s-Impulsen. Die Impulse der Impulsfolge  $h_1 + h_5 + \cdots$  erscheinen immer dann, wenn die halbe Ziffernzeit der ersten Dualziffer jeder Tetrade verstrichen ist. Ein etwas anderes Ausführungsbeispiel dieser Schalteinrichtung zeigt Fig. 4,1. Hier wird zur Löschung des Übertrags-Flip-Flops 45 ein Korrekturaddiator und zur Überführung des tetradischen Übertrags in den Übertrags-Flip-Flop 48 des Hauptaddiators die sich zeitlich mit den ersten Synchronisierimpuls s jeder ersten Dualziffer in den Tetraden genau deckende Impulsfolge  $s_1 + s_5 + \cdots$ verwendet. Als Korrekturaddiator ist dann dieselbe Ausführungsform des Addiator-Subtraktors zu verwenden, wie in Fig. 4 für den Hauptaddiator dargestellt ist. Dies ist durch die Konjunktions- und Disjunktionsschaltungen 50, 51, 52, 53, 54 mit den Eingängen 20, 21, 55, 56, 57, 58, 59, 60 in Fig. 4, 1 dar-

Die Schaltgröße  $\ddot{u}_{nk}$  am Ausgang der den Übertrag in die nächste Stelle erzeugenden Disjunktion  $\bf 54$ liefert dann am Ende der letzten Dualziffernzeit jeder Tetrade bereits allein eine eindeutige Aussage darüber, ob ein Übertrag in die nächste Tetrade erfolgt oder nicht.  $\ddot{u}_{n\,k}$  ist als Schaltgröße an das Gatter 61 geführt, das mit derselben Impulsfolge  $s_1 + s_5 + \cdots$  bei Koinzidenzbedingung den Übertrags-Flip-Flop **48** des Hauptaddiators einschaltet. Als Korrekturentscheid wurde weiter vorn die logische Schaltung, die dem Ausdruck

$$S_1 \cdot S_2 + S_1 \cdot S_3 + {n-1}$$

entspricht, angegeben. Es muß noch ein Zeitpunkt festgelegt werden, in dem dieser Entscheid zu erfolgen hat. In unserem Beispiel ist das Schieberegister vierstellig ausgeführt, wodurch in den vier Flip-Flops für das Schieberegister der Summentetrade am Tetradenende die Dualstellen  $S_1$  bis  $S_4$  der Summentetrade und 60 bei  $\ddot{u}_n$  im Summenaddiator der Übertrag in die nächste Tetrade zur Verfügung stehen. Die Dualstelle mit der niedrigsten Wertigkeit S4 ist jedoch korrigiert und unkorrigiert gleich, da nur »0« addiert oder subtrahiert wird. Sie wird zum Korrekturentscheid nicht benötigt, so daß sie bereits ins Hauptspeicherwerk eingelaufen sein kann, bevor der Korrekturentscheid stattfindet. Somit sind die Schieberegister nur dreistellig auszuführen. Man kann jedoch die Stellenzahl der Schieberegister sogar auf zwei Ursache der Notwendigkeit einer neuen Korrektur- 70 Stellen reduzieren. Während der vierten Dualstellenzeit der Tetrade steht nämlich  $S_1$  am Ausgang **62** des Hauptaddiators,  $S_2$  am Flip-Flop **63** und  $S_3$  am Flip-Flop **64** des Schieberegisters **7**.  $S_3$  würde erst mit dem Synchronisierimpuls s am Ende der Dualziffernzeit in dieser Form in das Hauptspeicherwerk eingetragen 5 werden. Der Korrekturentscheid ist daher vorher durchzuführen, und auch die richtige Dualziffer S. (korrigiert oder unkorrigiert) ist dem Speicher zuzuführen. Es kann dann ein vor dem die Tetrade beendenden Synchronisierimpuls s liegender  $h_a$ -Impuls 10 Verwendung finden. Dieser Impuls erscheint in der letzten Dualstellenzeit jeder Tetrade, und zwar zweckmäßig in der zeitlichen Mitte zweier Synchronisierimpulse s. Der auf h<sub>4</sub> folgende Synchronisierimpuls muß bereits eingeschwungene Schaltgrößenzustände is vorfinden, während andererseits  $h_4$  die vom vorigen Synchronisierimpuls geschalteten Schaltzustände verarbeiten muß. Ist zu korrigieren, dann schaltet dieser  $h_4$ -Impuls einen Flip-Flop 65 ein, der eine Steuerung derart bewirkt, daß die aus dem Schieberegister 12 20 auslaufenden Ziffern ins Hauptspeicherwerk gelangen. Wird dieser Flip-Flop nicht geschaltet, dann läuft der Inhalt des Schieberegisters 7 in den Hauptspeicher. Diese Auswahlsteuerung wird entsprechend dem logischen Ausdruck

### 66.67+66.68

mit 66 und 66 als Aussage des Flip-Flops 65, 67 als Aussage des Flip-Flops 69 vom Schieberegister 12 30 und 68 als Aussage des Flip-Flops 61 des Schieberegisters 7 durch zwei zweifache Konjunktionen 70 und 71 und eine zweifache Disjunktion 72 bewirkt. Ein in der Mitte der dritten Dualstellenzeit jeder Tetrade erscheinender Impuls  $h_3$  löscht Flip-Flop 65 wieder, 35 nachdem die korrigierten oder unkorrigierten Dualstellen  $S_3$ ,  $S_2$  und  $S_1$  der Summentetrade in den Speicher eingelaufen sind. Eine andere Ausführungsform der Schaltung des Flip-Flops 65 zeigt Fig. 4,2. Der Korrekturentscheid  $K_e$  schaltet mit Impuls  $h_4$  den 40 Flip-Flop 65 auf L, wenn zu korrigieren ist, und der durch einen Negator 70 negierte Korrekturentscheid Ke schaltet den Flip-Flop 65 mit Impuls h4 auf. Null, wenn nicht zu korrigieren ist. Ist z. B. mehrere Male hintereinander nicht zu korrigieren, dann wird stets 45 ein Impuls auf dieselbe Flip-Flop-Seite gegeben, und der Flip-Flop 65 bleibt in seiner ursprünglichen Lage. Bei dreistelligen Schieberegistern kann die Auswahl der richtigen Summentetradenstelle auch so vorgenommen werden, daß stets der Inhalt des Schiebe- 50 registers 7 in das Hauptspeicherwerk einläuft, daß aber, wenn zu korrigieren ist, der Inhalt des Schieberegisters 12 mit dem Impuls  $h_4$  über beispielsweise Gatterschaltungen in das Schieberegister 7 übergeführt wird. 55

#### PATENTANSPRUCHE:

1. Rechenwerk mit zwei hintereinandergeschalteten Binär-Addiatoren-Subtraktoren mit nachgeschalteten Schiebelinien für die Addition bzw. Subtraktion zweier Dezimalzahlen mit Korrektur der in einem Binär-Addiator-Subtraktor gebildeten Summe oder Differenz zweier als Tetraden 65 verschlüsselter Dezimalzahlen, wobei sowohl die Dezimalzahl als auch die Dualziffern der Tetraden nacheinander in das Rechenwerk einlaufen, dadurch gekennzeichnet, daß die unkorrigierte und die korrigierte Summe gleichzeitig gebildet werden, in 70

dem einem Eingang des Korrektur-Addiator-Subtraktors (8) ungesteuert ein Korrekturwert zugeleitet wird und ein im Korrektur-Addiator-Subtraktor (8) erzeugter und gespeicherter Übertrag durch Umschalten des Übertrags-Flip-Flops (45) mit einer Impulsfolge den Übertrags-Flip-Flop (48) vom Hauptaddiator-Subtraktor (3) einschaltet, wodurch der Übertrag in die nächste Tetrade eingetragen wird und über logische Schaltkreise, die den logischen Ausdruck

$$K_e = S_1 (S_2 + S_3) + \ddot{u}_{n-1}$$

und dessen Negation realisieren, den Auslauf der korrigierten oder unkorrigierten Summe bzw. Differenz aus den Schieberegistern (7, 12) steuert.

- 2. Rechenwerk nach Anspruch 1, dadurch gekennzeichnet, daß die Auswahl der korrigierten oder unkorrigierten Summentetrade dadurch erfolgt, daß stets nur der Inhalt ein und desselben Schieberegisters (7 oder 12) in Serie nach der Hauptspeicherwerkbahn (1) auslaufen kann, wobei in dieses Schieberegister (7 oder 12) nötigenfalls der Inhalt des anderen Schieberegisters (12 oder 7) vorher übergeführt wird.

- 3. Rechenwerk nach Anspruch 1, dadurch gekennzeichnet, daß die wahlweise Umschaltung des Addiator-Subtraktors (3) auf Addition oder Subtraktion durch zwei über Steuerleitungen gelieferte Schaltgrößen (20 und 21) erfolgt, wobei diese an je zwei Und-Schaltungen (22, 24 und 23, 25) führen, die die Ein- und Ausschaltung des den Übertrag in die nächste Dualstelle bildenden Flip-Flops (19) steuern, indem bei Addition mit der Konjunktion (22) der beiden Dualstellen der Summanden und der die Addition markierenden Schaltgröße (20) der Übertrags-Flip-Flop (19) eingeschaltet wird und erst mit der Konjunktion (24) der beiden negierten Summandendualstellen mit der Schaltgröße (20) der Übertrag wieder ausgeschaltet wird, bei Subtraktion jedoch mit der Konjunktion (23) der negierten Dualstelle des Minuenden, der Dualstelle des Subtrahenden und der die Subtraktion markierenden Schaltgröße (21) der Übertrags-Flip-Flop (19) eingeschaltet und mit der Konjunktion (25) der Dualstelle des Minuenden der negierten Dualstelle des Subtrahenden und der die Subtraktion markierenden Schaltgröße (21) der Übertrags-Flip-Flop (19) wieder auf »0« geschaltet wird.

- 4. Rechenwerk nach Ansprüchen 1 und 3, dadurch gekennzeichnet, daß zur Löschung des tetradischen Übertrags im Übertrags-Flip-Flop (45) des Korrekturaddiators (8) und zu seiner Überführung in den Übertrags-Flip-Flop (48) des Haupt-Addiator-Subtraktors (3) eine sich zeitlich mit dem die erste Dualstelle jeder Tetrade einleitenden Synchronisierimpuls (s) deckende Impulsfolge  $(s_1 + s_5 + \cdots)$  Verwendung findet.

5. Rechenwerk nach Ansprüchen 1 bis 4, dadurch gekennzeichnet, daß die Schieberegister (7 und 12) je zwei Dualstellen fassen und die niedrigste Tetradenstelle bereits ins Hauptspeicherwerk (1 und 2) gelaufen ist, ehe der Korrekturentscheid getroffen wird.

6. Rechenwerk nach Ansprüchen 1 bis 5, dadurch gekennzeichnet, daß ein zeitlich in der letzten Dualstellenzeit jeder Tetrade liegender Impuls  $(h_4)$  die Auswahl der richtigen Tetradenwerte einleitet.

7. Rechenwerk nach Ansprüchen 1 bis 6, dadurch gekennzeichnet, daß die von der logischen Schaltung

$$(S_1 \cdot S_2 + S_1 \cdot S_3 + \ddot{u}_{n-1} = K_e)$$

gelieferte Aussage, ob zu korrigieren ist, von einem Flip-Flop (65) so lange festgehalten wird, bis die Tetrade ins Hauptspeicherwerk (1 und 2) übergeführt ist.

8. Rechenwerk nach Ansprüchen 1 bis 7, da- 10 durch gekennzeichnet, daß ein während der dritten Dualstellenzeit jeder Tetrade erscheinender Impuls (h<sub>3</sub>) den Flip-Flop (65) wieder löscht.

9. Rechenwerk nach Ansprüchen 1 bis 9, dadurch gekennzeichnet, daß an die Einschaltseite 15 des Flip-Flops (65) die Aussage des Korrekturentscheids (K<sub>e</sub>) und an die Ausschaltseite des Flip-

Flops (65) der negierte Korrekturentscheid ( $K_e$ ) geführt ist in der Form, daß eine Aussage entsprechend der L in Koinzidenz mit einem kurzzeitigen Impuls die zugehörige Flip-Flop-Seite auf L schaltet und daß der kurzzeitige Impuls in der vierten Dualstellenzeit der Tetrade ( $h_4$ ) erscheint.

In Betracht gezogene Druckschriften:

USA.-Patentschrift Nr. 2861740;

»Elektronic Engineering«, 1953, Oktoberheft,

S. 410 bis 416;

»Elektronic Engineering«; 1953, Septemberheft,

S. 422;

»Arithmetic Operations in Digital Computers«, D. van Nostrand Comp., Inc., New York 1955, S. 239/240

Hierzu 1 Blatt Zeichnungen

Fig.1

Fig.3

Fig. 4, 1

Fig. 4, 2

| Ke | 6 | 66 | 66 | 65 |

| 70 | 65 | 65 |